Vhdl Program For 8 Bit Up Down Counter

VHDL Tutorial: Learn by Example. (8 rows by 8. This VHDL program is a structural description of the interactive Three to Eight Decoder. Vhdl Program For 8 Bit. Up vote 3 down vote Needs to operate off one clock edge Because your counter port has clk in it, we can assume you want the counter to count synchronous to the clock. Vhdl Program For 8 Bit Up Down Counter. 7/11/2017 0 Comments Mod-n Synchronous Counter, Cascading Counters, Up-Down Counter Digital Logic Design Engineering Electronics Engineering Computer Science. Synchronous Counter. In the previous Asynchronous binary counter tutorial, we saw that the output of one counter stage is connected directly to the clock input of the. Clock Divider is also known. Vhdl Program For 8 Bit Up Down Counter 74193. Ic 74193 down counter 4 bit, vhdl program for 4 bit up counter, 4 bit counter using ic 7493 theory. UP-DOWN COUNTER library IEEE. 8 bit leading zero count vhdl program? 4 bit Synchronous UP counter. The test bench program used for testing the design is given below. The test bench program used for testing the design is given below.

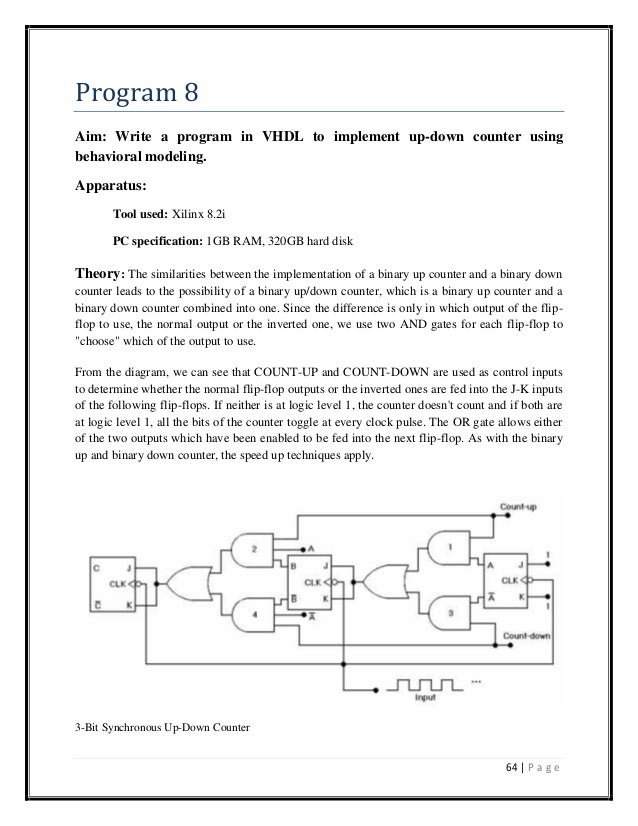

I am a complete beginner in VHDL, so I was hoping that someone could help me with this project I am working on.

I need to realize rectangular pulse generator which frequency can be changed in the range 0 through 255. Frequency value in kHz must be shown binary on 8 LED diodes on the development board. For adjusting the output pulse frequency two buttons are used(incrementing/decrementing). When the button is held down for more than a second, the frequency is automatically incrementing/decrementing.

I wrote some code, but in Xilinx I get a ton of warnings. Can somebody explain them to me?

Code for frequency divider:

Code for state machine:

Warnings:

Thanks in advance.

A #60 helped, but it wasn't gone. Keihin cr special carburetor tuning manually. I eventually found that a #50 cleared up the issue completely. If the bog is present, but not severe, try jumping down in smaller increments until the bog is gone. In the case of the aforementioned 2007 CRF250R, It had the stock #70 leak jet installed.

1 Answer

The second process of your state machine is the culprit. A process should be either synchronous or combinational, not a mix of both.

A synchronous process has this form:

Combinational processes do not use reset or clk. When using combinational processes, make sure all signals are assigned in every paths, i.e. every if has an else, every case an others. Failing to assign a signal in one of the paths will yield a latch.

Latches are evil's incarnation to anyone but experts. Any design using latches will most likely not behave the same on hardware as it does on simulation.

Jonathan DroletJonathan Drolet